74LS112 datasheet

|

74LS112 manufactured by:

|

|

|

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop with Preset/ Clear/ and Complementary Outputs Others with the same file for datasheet: DM74KS112AM, DM74LS112AN |

Download 74LS112 datasheet from Fairchild Semiconductor |

pdf 56 kb |

|

|

Dual J-K Negative-edge-triggered Flip-Flops(with Preset and Clear) |

Download 74LS112 datasheet from Hitachi Semiconductor |

pdf 80 kb |

|

|

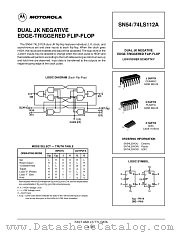

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP Others with the same file for datasheet: SN54LS112A, SN54LS112J, SN74LS112D, SN74LS112N |

Download 74LS112 datasheet from Motorola |

pdf 153 kb |

|

|

DUAL J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS WITH PRESET AND CLEAR Others with the same file for datasheet: SN54LS112, SN54LS112AFK, SN54LS112AW, SN54LS112FK, SN54LS112W |

Download 74LS112 datasheet from Texas Instruments |

pdf 308 kb |

| 74LS11 | View 74LS112 to our catalog | 74LS12 |